石英晶振設(shè)計(jì)備注

串聯(lián)與并聯(lián)

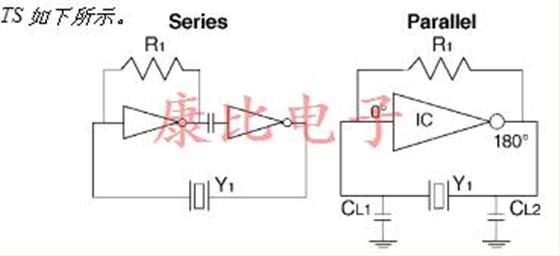

"串聯(lián)"諧振晶體用于振蕩器反饋環(huán)路中不含無功分量的電路中."并聯(lián)"諧振晶體用于在振蕩器反饋環(huán)路中包含無功分量(通常是電容器)的電路中.這種電路依賴于無功元件和晶體的組合,以實(shí)現(xiàn)必要的相移,從而啟動(dòng)并保持在額定頻率的振蕩.兩個(gè)這樣的電路的基本描述

圖1

負(fù)載電容

這是指晶振外部的電容,包含在振蕩器電路的反饋環(huán)路中.如果應(yīng)用需要一個(gè)"并聯(lián)"諧振晶體,則必須指定負(fù)載電容的值.如果應(yīng)用需要一個(gè)"串聯(lián)"諧振晶體,則負(fù)載電容不是一個(gè)因素,也不需要指定.負(fù)載電容是PCB上晶振引腳上測量或計(jì)算的電容值.

頻率容差

頻率容差指在特定溫度(通常為+25°C)下與標(biāo)稱值的允許偏差,單位為ppm.

頻率穩(wěn)定度

頻率穩(wěn)定性指額定溫度范圍內(nèi)的容許偏差,單位為百萬分之幾(PPM).偏差以+25°C時(shí)測得的頻率為基準(zhǔn).

老化

老化是指晶體單位經(jīng)歷的頻率隨時(shí)間的累積變化.影響時(shí)效的因素有過高的驅(qū)動(dòng)電平,各種熱效應(yīng),線材疲勞和摩擦磨損.采用低工作環(huán)境和最小驅(qū)動(dòng)電平的電路設(shè)計(jì)將降低老化率.

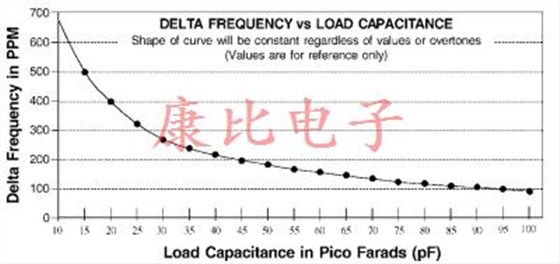

可拉性可拉性是指晶體單元的頻率從自然諧振頻率(fr)到負(fù)載諧振器頻率的變化(fL),或者從一個(gè)負(fù)載諧振頻率到另一個(gè)負(fù)載諧振頻率.見圖6在給定的負(fù)載電容值下,給定晶體單元表現(xiàn)出的可拉性的量是并聯(lián)電容(CO)和運(yùn)動(dòng)電容的函數(shù)1)的晶體單元.

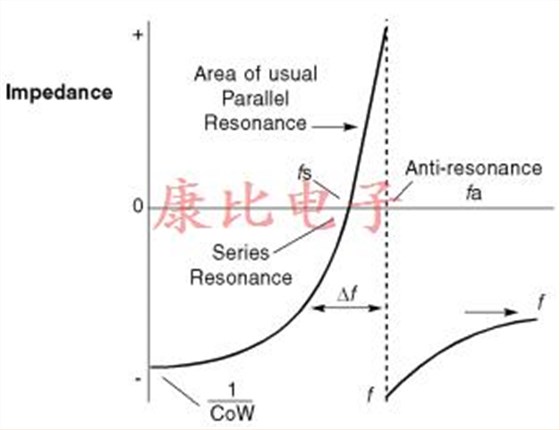

圖2

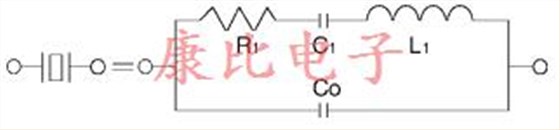

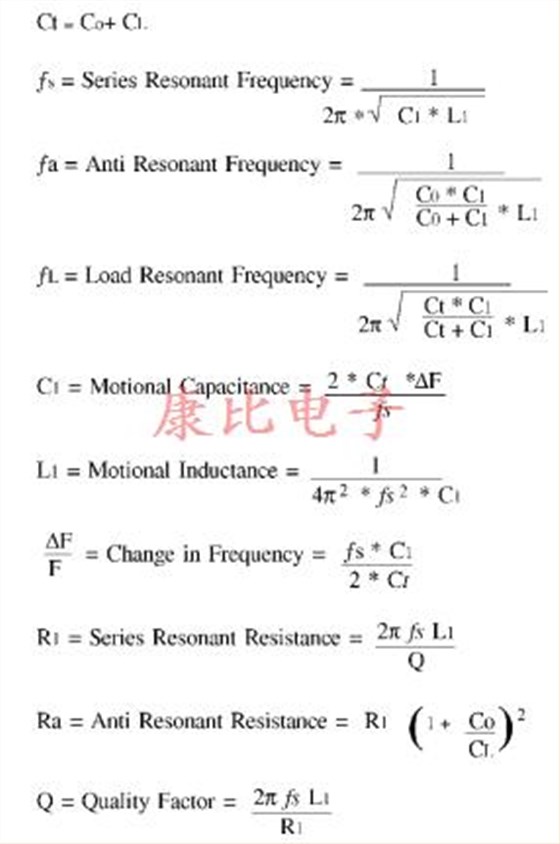

等效電路等效電路,如圖7,是在自然諧振頻率下操作時(shí)石英晶振單元的電描述.CO或并聯(lián)電容表示晶體電極的電容加上保持器和引線的電容.R1,c1,和我1構(gòu)成晶體的“運(yùn)動(dòng)臂”,稱為運(yùn)動(dòng)參數(shù).運(yùn)動(dòng)電感(L1)表示晶體單元的振動(dòng)質(zhì)量.運(yùn)動(dòng)電容(c1),表示石英的彈性和電阻(R1),表示發(fā)生在石英內(nèi)的體積損失.

圖3

阻抗/電抗曲線晶體具有兩個(gè)零相位頻率,如圖82.第一個(gè)或兩者中較低的一個(gè)是串聯(lián)諧振頻率,表示為(f此時(shí),晶體在電路中表現(xiàn)為電阻性,阻抗最小,電流最大.隨著頻率增加超過串聯(lián)諧振點(diǎn),貼片晶振在電路中表現(xiàn)為感性.當(dāng)運(yùn)動(dòng)電感和并聯(lián)電容的電抗消除時(shí),晶體處于反諧振頻率,表示為(f

圖4

品質(zhì)因數(shù)(Q)

晶體單位的“Q”值是單位相對質(zhì)量或振蕩效率的量度.晶體單元可達(dá)到的最大穩(wěn)定性取決于“Q”值.在圖8

以上,串聯(lián)和并聯(lián)頻率之間的間隔稱為帶寬.帶寬越小,Q值越高,電抗斜率越陡.外部電路元件電抗的變化對高Q晶體的影響較小(較小的“可拉性”),因此這樣的器件更穩(wěn)定.

負(fù)載電容的計(jì)算

如果并聯(lián)版本的電路配置如圖5所示,則可以通過下式計(jì)算負(fù)載電容:cL1*cL

2cL=cL1+cL2+雜散

CSTRAY包括的微處理器芯片的引腳間輸入和輸出電容晶體1以及晶體2引腳,加上任何寄生電容.根據(jù)經(jīng)驗(yàn),CSTRAY可以假定等于5.0pF.因此,如果CL1=CL2=50pF,CL=30pF.

調(diào)整靈敏度

調(diào)整靈敏度是負(fù)載電容值增量變化時(shí)增量小數(shù)頻率變化的量度.調(diào)整靈敏度(S)用ppm/pF表示,計(jì)算公式如下:S=c1

*10000002*cT

2其中(cT)是co和c的和L

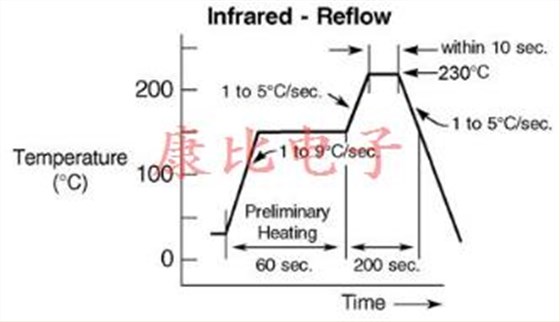

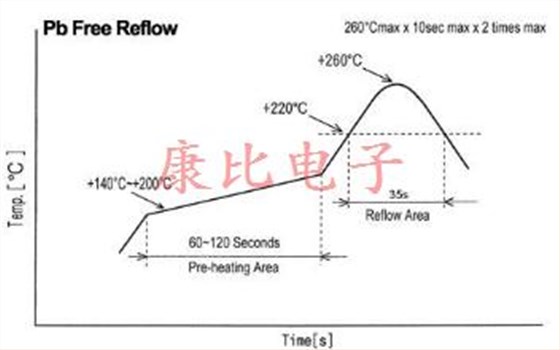

表面貼裝器件的回流焊SMD晶振單元的安裝通常通過焊料回流來完成,在圖9

要么通過紅外加熱,要么通過氣相.下圖描述了兩種方法中每種方法的推薦時(shí)間和溫度:

TXC晶振,貼片晶振,7M晶振

TXC晶振,貼片晶振,7M晶振 TXC晶振,貼片晶振,7S晶振

TXC晶振,貼片晶振,7S晶振 TXC晶振,貼片晶振,7A晶振

TXC晶振,貼片晶振,7A晶振 微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體

微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體